案例&资讯

缓存应用程序ST-MRAM流程和性能演示

来源:宇芯有限公司 日期:2020-01-08 09:46:13

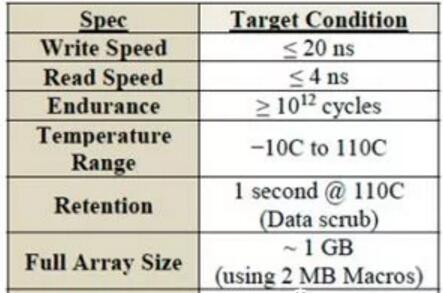

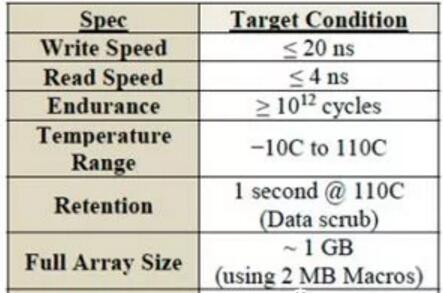

英特尔显示了2MB ST-MRAM阵列的L4缓存级应用程序性能和可靠性。这要求在工业操作温度范围内具有高密度,高带宽和高耐久性。表I中所显示STT-MRAM的L4高速缓存应用程序所需的规范。

表I.L4缓存应用程序中STT-MRAM的目标规范。

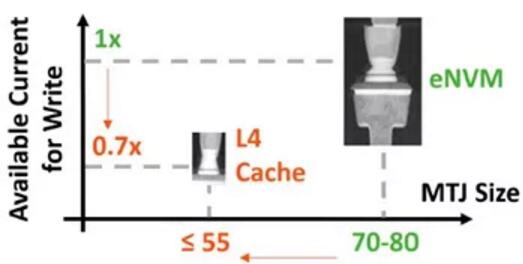

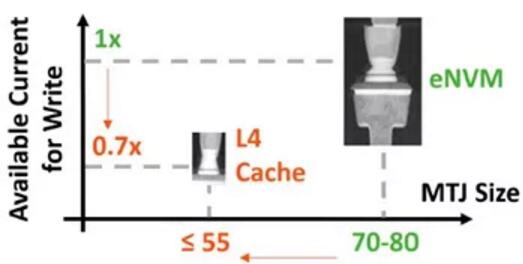

要替换SRAM或eDRAM,需要大于256GB/秒的带宽和大于10Mb/mm2的阵列密度。如图1所示的密度要求限制了位单元的间距和访问晶体管的尺寸,因此限制了STT写入可用的最大的电流,因此将数据保留的时间在110°C的最高工作温度下限制为“1秒”。

图1.与eNVM应用程序相比,L4缓存所需的位单元间距的要更小。

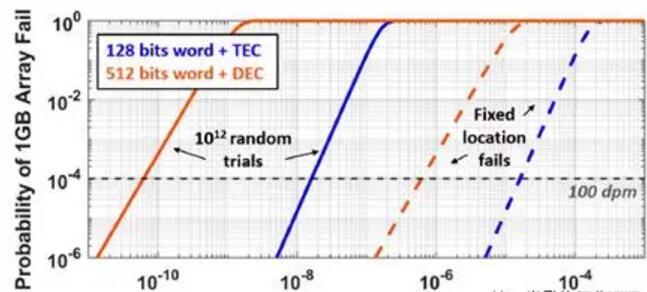

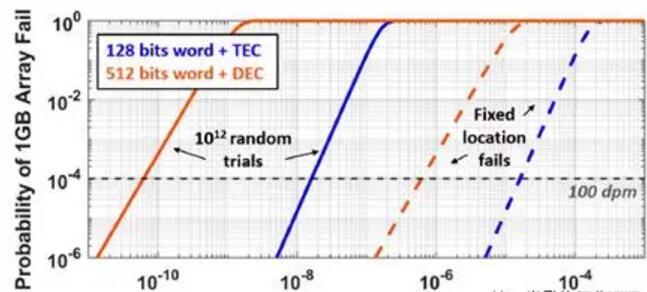

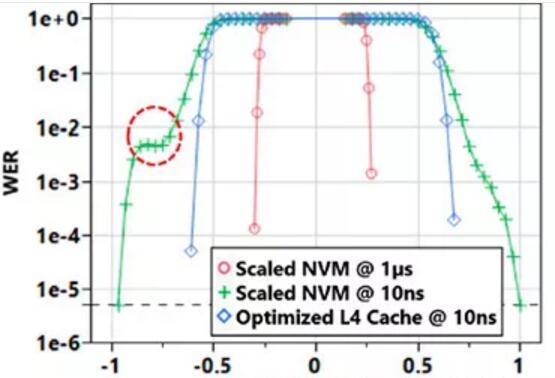

另一方面要求1e12个周期的写入耐久度会限制最大写入电流,以确保耐久度保持在ECC可校正的范围内。为了实现小于100dpm的可接受的ECC可校正的1Gb阵列误码率(BER)(1Gb阵列失败概率为1e-4),所需的固定和随机写入错误率(WER)错误如图2所示。两种不同的体系结构,具有三重纠错(TEC)的128b字节和具有双重纠错(DEC)的512b字节。对于1e12写事件,随机BER需要为1e-8至1e-10。

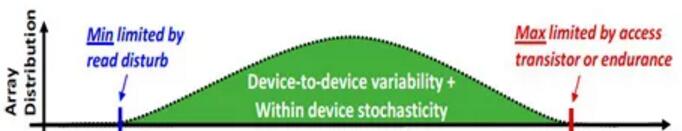

55nmMTJ需要可靠的堆栈优化和反应离子蚀刻(RIE)工艺。发现有缺陷的故障时会降低电阻和TMR的短路模式(硬性短路和软性短路)。融合了时间=0时的失败位。可接受的WER电平和较短的写入脉冲需要使MTJ过驱动,受可用驱动电流和耐久性考虑因素的限制,如下列图3所示。

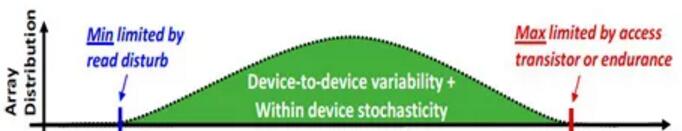

图3.写入电流分布受可用驱动电流和耐用性要求的限制,以及读取干扰的要求。

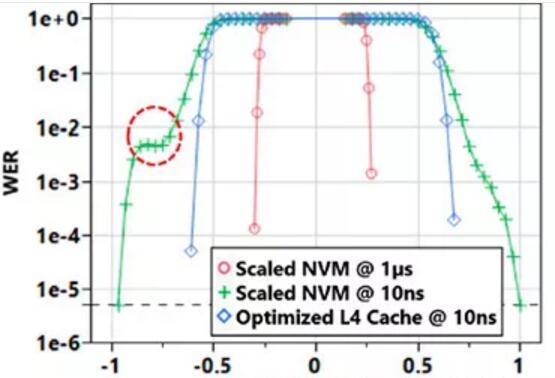

最小电流是读取干扰所需的电流,随着温度的降低而提高,因此读取干扰选定在测量温度为95℃下,可以通过1e7读取完整的字节来获取。图14中显示了NVM应用程序和经过优化的L4高速缓存设备(具有10ns写脉冲)缩放的MTJ的写错误率曲线,如蓝色显示。

WER的关键条件是在-10°C,但是随着温度的升高,MJT变得更容易写入,而在更高的温度下VCC可以降低。由于缺陷的热激活会导致MgO介电击穿,因此在105°C下进行了耐久性测试。

关键词:ST-MRAM

表I.L4缓存应用程序中STT-MRAM的目标规范。

要替换SRAM或eDRAM,需要大于256GB/秒的带宽和大于10Mb/mm2的阵列密度。如图1所示的密度要求限制了位单元的间距和访问晶体管的尺寸,因此限制了STT写入可用的最大的电流,因此将数据保留的时间在110°C的最高工作温度下限制为“1秒”。

图1.与eNVM应用程序相比,L4缓存所需的位单元间距的要更小。

另一方面要求1e12个周期的写入耐久度会限制最大写入电流,以确保耐久度保持在ECC可校正的范围内。为了实现小于100dpm的可接受的ECC可校正的1Gb阵列误码率(BER)(1Gb阵列失败概率为1e-4),所需的固定和随机写入错误率(WER)错误如图2所示。两种不同的体系结构,具有三重纠错(TEC)的128b字节和具有双重纠错(DEC)的512b字节。对于1e12写事件,随机BER需要为1e-8至1e-10。

图2.固定位置失败(虚线)和随机失败(稳定)的允许BER的ECC计算与1Gb阵列失败概率(ECC不可纠正)相比,假定具有三重纠错(TEC)的128b字节(蓝色)或具有三次错误校正的512b字节双重错误校正(DEC)(橙色)。

55nmMTJ需要可靠的堆栈优化和反应离子蚀刻(RIE)工艺。发现有缺陷的故障时会降低电阻和TMR的短路模式(硬性短路和软性短路)。融合了时间=0时的失败位。可接受的WER电平和较短的写入脉冲需要使MTJ过驱动,受可用驱动电流和耐久性考虑因素的限制,如下列图3所示。

图3.写入电流分布受可用驱动电流和耐用性要求的限制,以及读取干扰的要求。

最小电流是读取干扰所需的电流,随着温度的降低而提高,因此读取干扰选定在测量温度为95℃下,可以通过1e7读取完整的字节来获取。图14中显示了NVM应用程序和经过优化的L4高速缓存设备(具有10ns写脉冲)缩放的MTJ的写错误率曲线,如蓝色显示。

图4.不同设备的写入错误率(WER),以蓝色显示优化的L4缓存MTJ。

WER的关键条件是在-10°C,但是随着温度的升高,MJT变得更容易写入,而在更高的温度下VCC可以降低。由于缺陷的热激活会导致MgO介电击穿,因此在105°C下进行了耐久性测试。

关键词:ST-MRAM

上一篇文章:预期Nand-flash内存需求市场及价格涨

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin、来杨Lyontek、ISSI、CYPRESS等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin、来杨Lyontek、ISSI、CYPRESS等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。