案例&资讯

Cortex‐M3和Cortex‐M0是否都能位带操作

来源:宇芯有限公司 日期:2019-07-15 11:21:03

在对stm32l011f4的编程中考虑到stm32有位带操作,想尝试一下是否可以操作,先付上位带操作代码

Cortex‐M0的位带操作代码

//IO输出方向设置

#define SDA_IN() {GPIOA->MODER&=0XFFF1FFFF;} //PA_10设置成输入

#define SDA_OUT() {GPIOA->MODER&=0XFFF5FFFF;} //PA_10设置成输出

// SDA = PA_10;SCL = PA_9

#define IIC_SCL PAout(9)

#define IIC_SDA PAout(10)

#define READ_SDA PAin(10)

MODER寄存器为IO端口功能寄存器

Cortex‐M3的位带操作代码

//IO输入输出设置

#define SDA_IN() {GPIOB->CRH&=0XFFFF0FFF;GPIOB->CRH|=8<<12;}

#define SDA_OUT() {GPIOB->CRH&=0XFFFF0FFF;GPIOB->CRH|=3<<12;}

//SDA=PB_11;SCL=PB_10

#define IIC_SCL PBout(10) //SCL

#define IIC_SDA PBout(11) //SDA

#define READ_SDA PBin(11) //SDA设为输入

CRH为Cortex‐M3的端口功能寄存器

但是由于Cortex‐M0编译存在问题,通过对规格书的查询对比发现Cortex‐M0芯片不支持位带操作

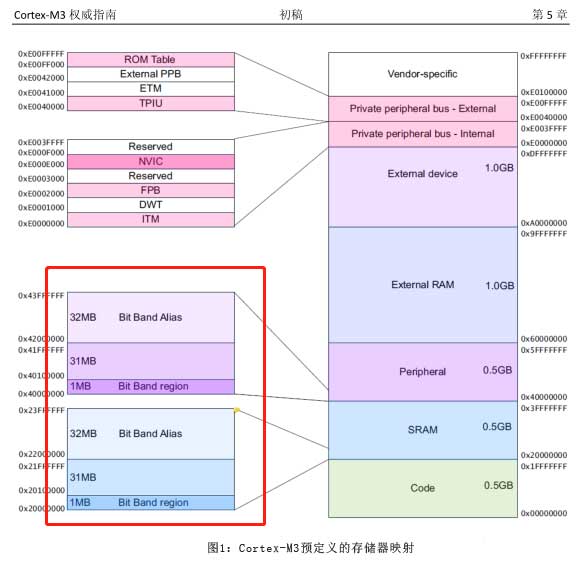

Cortex‐M3存在端口映射区是可以支持位带操作。

Cortex‐M0不存在端口映射区是不支持位带操作。

因此在编写Cortex‐M0的程序时,可以不考虑位带操作。

上一篇:在网络设计系统如何应用SRAM芯片

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin、来杨Lyontek、ISSI、CYPRESS等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin、来杨Lyontek、ISSI、CYPRESS等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。