案例&资讯

生产STT-MRAM难度大

来源: 日期:2018-01-17 15:07:45

对大多数公司来说,生产 MRAM 说起来容易,实际做起来却更难。MRAM 涉及到开发新的材料、集成方法和设备。

嵌入式 MRAM

它的工艺流程也与传统内存的不一样。正常情况下,MRAM 工艺是从传统晶圆厂开始的,代工供应商会在这里生产带有电路的标准 CMOS 晶圆,这就是所谓的生产线前道工序(FEOL)。其中的电路可以集成一种晶体管方案或一个微控制器(MCU)这样的器件。

然后,该器件和/或一个基板会被送到被称为生产线后道工序(BEOL)的另一处晶圆厂设施。在这里,金属层和微细的铜导线会被加工装配到该器件上。

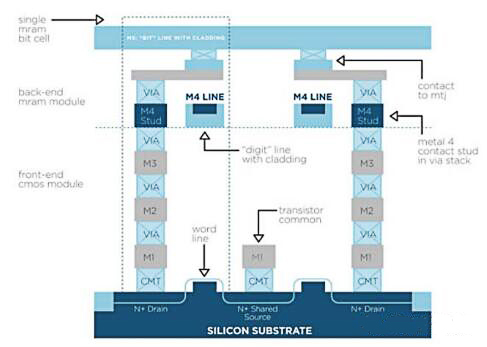

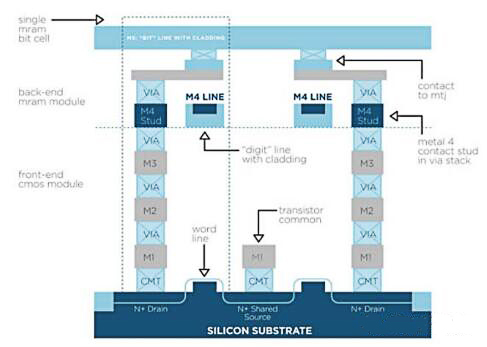

STT-MRAM 是在晶圆厂的 BEOL 工序中生产制造的。实际上,STT-MRAM 内存层构建于芯片中一个金属层的触点或通孔之上,比如 M4 或其它金属层。

嵌入式 MRAM

DRAM 和闪存则相反,是在内存晶圆厂的 FEOL 工序中加工的。在 FEOL 工序中,传统内存加工时的温度更高。

但是 MRAM因为磁性薄膜很薄,无法承受更高的温度,所以 MRAM 在 BEOL 工序制造,这时候的温度要低得多。Applied 的 Ping 说:“磁性薄膜非常薄,你不能给它提供非常高的温度。”

生产制造 STT-MRAM 是一个精细的过程。如果步骤不严格遵守,就会出问题。短缺的情况常常发生,就会影响产量。解决缺陷问题也很具挑战性。

首先,STT-MRAM 在以下部分需要三个掩模步骤:底部电极、顶部电极和 MTJ 单元。第一步是沉积一层薄层材料,这会成为底部电极。然后就会遇到第一个难点——形成薄膜的堆叠。这种薄膜堆叠可能有 20 到 30 层。方法就是高精度地一层一层地沉积这些薄膜。

Ping 说:“这是一种非常薄的膜,厚度只有几埃。你要将它们堆叠起来以实现磁化作用的最大化。”

在某些情况下,STT-MRAM 是在一个使用各种工艺模组的封闭的集群工具中制造的。这些模组包含用于物理气相沉积(PVD)、退火和离子束蚀刻的专门腔室。

如果这种薄膜堆叠暴露在空气中,就会出现问题。“你需要在同一台机器中蚀刻和封装它。”Lam Research 副总裁 Thorsten Lill 说,“你不能将晶圆暴露在空气中。”

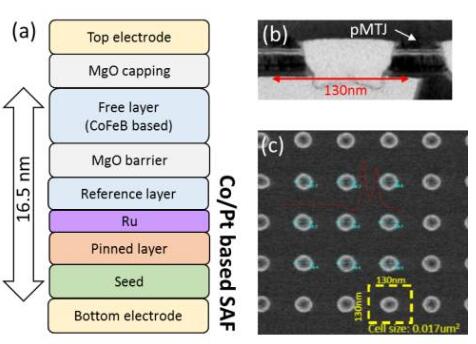

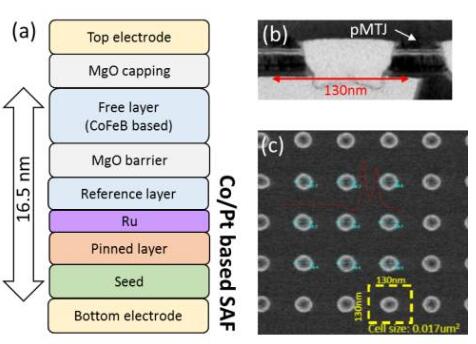

STT-MRAM 包含一个 MTJ 内存单元。MTJ 使用了基于氧化镁(MgO)的薄介电隧道势垒薄膜,它被夹在两层基于硼铁化钴(CoFeB)化合物的铁磁层之间。在工作时,电流会流过仅有大约 10 埃厚度的 MgO 薄膜。据 Applied Materials 的数据,CoFeB 层的厚度为 10 到 30 埃。

pMTJ 薄膜堆叠细节。(b) 和 (c) 展示了 pMTJ 阵列的横截面和顶视图,来自Applied Materials

在晶圆厂中,这种堆叠可以进行调节。Lam 的 Lill 说:“关于 MRAM 的有趣之处在于根据你构建这种堆叠的方法的差异,你可以得到更低或更高温度的器件。你可以让它像闪存或 SRAM。所有这些都可以通过调整这种堆叠办到。”

然后,对该薄膜堆叠执行退火,之后又是另一大难题——蚀刻。要得到预期大小和尺寸的 MTJ 堆叠,要在表面沉积一种抗蚀剂,然后再蚀刻。

STT-MRAM 没有使用的传统的反应离子束蚀刻(RIE)工具,因为这会破坏堆叠。行业实际使用了离子束蚀刻(IBE),即使用带电离子束蚀刻这些薄膜。

使用 IBE 时,离子束会撞击薄膜表面。“这是溅射方法。”Lill 说,“这被称为化学增强离子束蚀刻(chemically-enhanced ion beam etching)。第一代是纯惰性气体氩氙溅射。”

但 IBE 也面临着一些挑战。Applied 的 Ping 说:“离子束蚀刻器对间距有限制。当你的间距更小时,会出现阴影效应。这项技术还仍在开发之中。”

然后,在完成 IBE 之后,该器件就会被封装起来。在每一步,这个器件都要经历多种计量步骤。KLA-Tencor 客户参与高级总监 Neeraj Khanna 表示:“我们预计这些新架构将会推动发展对计量和检测的新要求。”

关键词:STT-MRAM

上一篇:STT-MRAM 的特性与难题

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin、来杨Lyontek、ISSI、CYPRESS等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。

关键词:STT-MRAM

上一篇:STT-MRAM 的特性与难题

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin、来杨Lyontek、ISSI、CYPRESS等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。