案例&资讯

DDR5芯片与DDR、GDDR、LPDDR的对比

来源:宇芯有限公司 日期:2017-12-04 15:18:52

2017年3月,JEDEC协会宣布将在2018年正式发布DDR5的技术规范。目前,DDR5的规范制定已经到0.5版本,会在DDR4的基础上数据速率和密度再翻一倍,单颗粒容量可达32Gb,并预计会在2020年开始商用。

DDR(Double Data Rate)是用于系统的RAM技术,其特点是高带宽、低延时。DDR总线每个Channel是64bit宽度,每根Data的管脚(DQ)可以进行读操作或写操作(不同时)。目前的最新标准是DDR4,数据线可以支持到3200MT/s,而DDR5是未来的技术,数据速率会再翻倍。

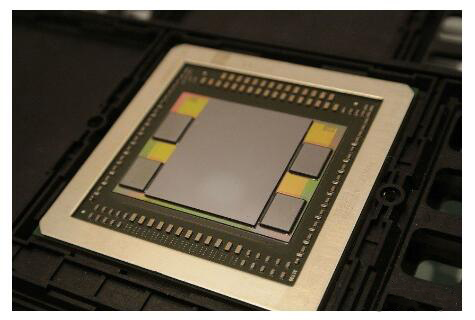

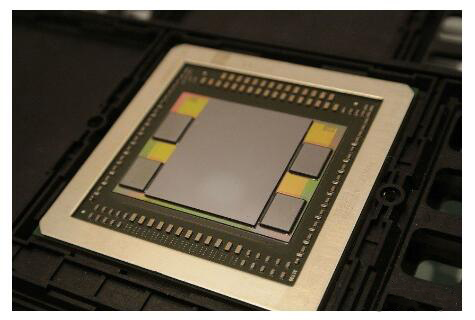

另外,DDR5还会采用HBM的封装以提高内存芯片的密度和通道数。High Bandwidth Memory (HBM) 技术最早来源于AMD、Hynix、UMC、Amkor、ASE等公司,是一种高速的3D封装的RAM接口技术。第一代的HBM技术在2013年被JEDEC协会采纳(JESD235标准),代表产品是AMD公司代号为Fuji的GPU芯片(下图);而其第二代的HBM2技术也在2016年被JEDEC协会采纳(JED235A标准),代表产品是nVidia公司的Tesla P100芯片。目前,第三代的HBM3技术也在开发过程中,并将用于未来的DDR5芯片上。

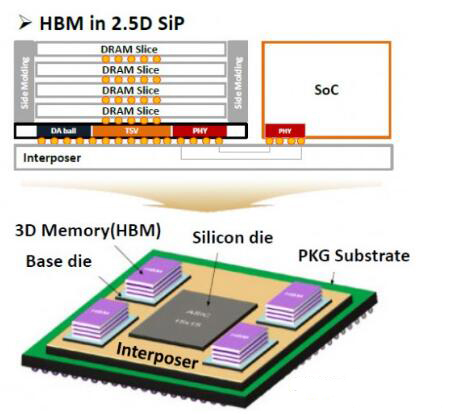

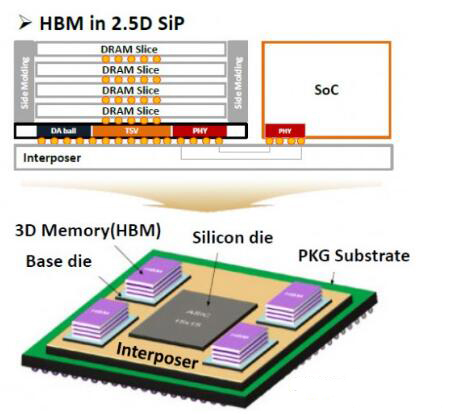

HBM技术可以把最多8层DRAM的Die堆叠起来,并通过TSV(Through-Silicon Vias:硅通孔)技术和内存控制器通过相应的Interposer互联起来。在HBM接口中,内存控制器和和不同的Die间采用独立的Channel进行互联,各个Channel间互相没有关系,因为可以进行独立的时序设计以提高数据传输速率。比如在采用4层Die堆叠、每个Die有2个Channel、每个Channel有128bit宽度时,如果采用4颗芯片,则总的数据位宽= 4(Stack)*4(Die)*2(Ch)*128(bit)= 4096bit。

关键词:DDR5

上一篇:单片机的片内存储器跟片外存储器的详解

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin、来杨Lyontek、ISSI、CYPRESS等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。

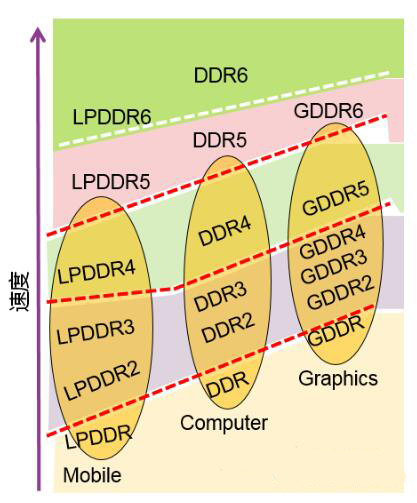

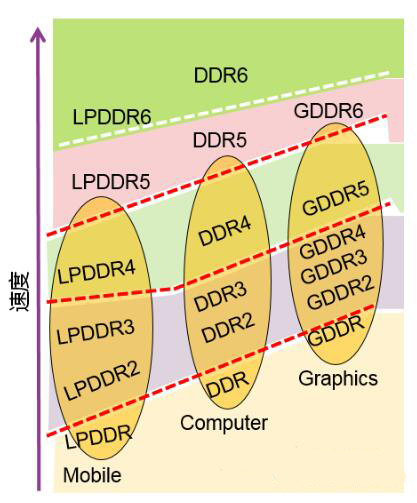

很多人会把DDR5和显卡上使用的GDDR5技术混淆,其实两者应用场合不同。下面这张图展示了目前三种主流内存技术(DDR、GDDR、LPDDR)的速度对比和应用场合。

DDR(Double Data Rate)是用于系统的RAM技术,其特点是高带宽、低延时。DDR总线每个Channel是64bit宽度,每根Data的管脚(DQ)可以进行读操作或写操作(不同时)。目前的最新标准是DDR4,数据线可以支持到3200MT/s,而DDR5是未来的技术,数据速率会再翻倍。

GDDR(Graphics Double Data Rate),是用于显示的RAM技术,其特点是高带宽、高延时。GDDR5技术实际来源于DDR3,只不过降低了电压,减少了位宽(但支持更多Channel),通过数据编码和读写线分开提高了数据速率(3G~6GT/s)。GDDR5已经使用了将近10年,目前最新的标准是GDDR6。

从数据速率上来说,GDDR更高,适合显示图像这种需要大数据量传输而对时延不太敏感的场合;而DDR技术由于延时小,所以更适合于CPU这种数据随机读取的场合。

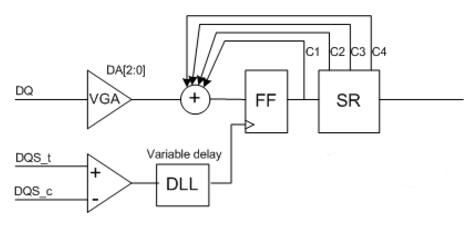

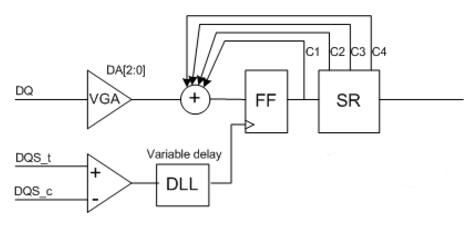

据内部可靠消息,由于DDR5的数据速率已经达到甚至超过了现在一些串行总线的数据速率,所以DDR5芯片的接收端还会采用在串行总线上广泛应用的可变增益放大器VGA(variable gain amplifier)、可变Delay(通过DLL实现)以及4阶DFE(decision feedback equalizer)均衡技术以优化采样位置和眼图的质量。下图是DDR5芯片接收端的设计架构。

另外,DDR5还会采用HBM的封装以提高内存芯片的密度和通道数。High Bandwidth Memory (HBM) 技术最早来源于AMD、Hynix、UMC、Amkor、ASE等公司,是一种高速的3D封装的RAM接口技术。第一代的HBM技术在2013年被JEDEC协会采纳(JESD235标准),代表产品是AMD公司代号为Fuji的GPU芯片(下图);而其第二代的HBM2技术也在2016年被JEDEC协会采纳(JED235A标准),代表产品是nVidia公司的Tesla P100芯片。目前,第三代的HBM3技术也在开发过程中,并将用于未来的DDR5芯片上。

HBM技术可以把最多8层DRAM的Die堆叠起来,并通过TSV(Through-Silicon Vias:硅通孔)技术和内存控制器通过相应的Interposer互联起来。在HBM接口中,内存控制器和和不同的Die间采用独立的Channel进行互联,各个Channel间互相没有关系,因为可以进行独立的时序设计以提高数据传输速率。比如在采用4层Die堆叠、每个Die有2个Channel、每个Channel有128bit宽度时,如果采用4颗芯片,则总的数据位宽= 4(Stack)*4(Die)*2(Ch)*128(bit)= 4096bit。

关键词:DDR5

上一篇:单片机的片内存储器跟片外存储器的详解

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin、来杨Lyontek、ISSI、CYPRESS等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。