案例&资讯

SRAM结构框图解

来源: 日期:2022-12-05 11:53:00

SRAM即静态RAM.它还由晶体管组成,SRAM它们通常被用作高速和静态特性Cache存储器。

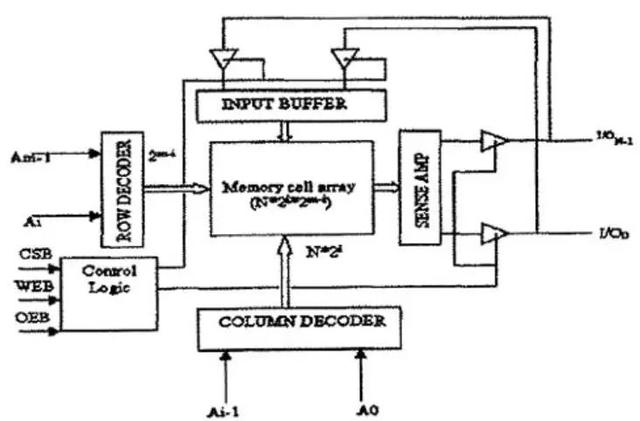

下图显示了一个SRAM结构框图。

由图中看出SRAM一般由存储单元阵型、地址译码器(包括行译码器和列译码器)、灵敏放火器、控制电路和缓存/驱动电路五部分组成。A0-Am-1为地址输入端,CSB.WEB和OEB为控制端,控制读写操作,为低电频有效1100-1100ON-1是数据输出端。存储阵列中的每个存储单元都与行列上的其他模块共享电连接,其中水平连接称为“字线”垂直方向信息流入和流出存储单元的连接称为“位线”。

根据输入地址,可以选择特定的字线和位线。字线和位线的交叉点是选定的存储单元。每个存储单元都是按照这种方法唯一选择的,然后进行读写操作。一些存储器设计为多个数据,如4位或8位,同时输入和输出。这样,将同时选择4个或8个存储单元进行读写操作。

在SRAM中,矩阵形式的存储单元阵型被翻译器和与外部信号的通信界面包围。存储单元阵型通常是方形或矩阵,以减少整个芯片面积,有利于数据存储。一个存储容量为4K位的SRAM例如,需要12条地址线来确保每个存储单元都能被选中(212=-4096)。如果存储单元阵型排列成只包括一列的长条,则需要12/4K位译码器,如果排成方形,包括64行和64列,那么只需要一个6/64位的行译码器和一个6/64位的行译码器。行、列译码器可分别排列在存储单元阵型的两侧。64行和64列有4096个交接点,每个点对应一个存储位置。

因此,将存储单元排列成方形比排列的长条应大大降低整个芯片的地面面积。除了奇特的形状和大范围外,存储单元排列成长条状的另一个缺点是,排列在排列上端的存储单元与数据输入/导出端之间的连接将变得非常长,特别是对于容积非常大的存储器,情况更为严重,连接延迟至少与其长度线性有关。连接时间越长,在线延迟就越大。因此,读写速度的降低和不同存储单元之间的连接延迟是不一致的,这是规划中需要避免的。

本文关键词:SRAM

宇芯有限公司自成立以来,我们专注于代理国内外各大知名品牌的半导体元器件,代理品牌有NETSOL、JSC、everspin代理、来杨Lyontek、ISSI、CYPRESS,VTI等多个品牌总代理资质,主要产品线为sram、mram、psram等其他存储器芯片,致力于为客户提供具有竞争优势的产品,是一家专业提供存储方案解决商。

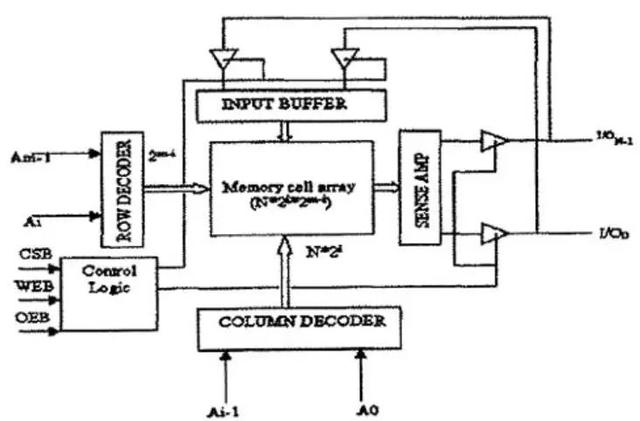

下图显示了一个SRAM结构框图。

由图中看出SRAM一般由存储单元阵型、地址译码器(包括行译码器和列译码器)、灵敏放火器、控制电路和缓存/驱动电路五部分组成。A0-Am-1为地址输入端,CSB.WEB和OEB为控制端,控制读写操作,为低电频有效1100-1100ON-1是数据输出端。存储阵列中的每个存储单元都与行列上的其他模块共享电连接,其中水平连接称为“字线”垂直方向信息流入和流出存储单元的连接称为“位线”。

根据输入地址,可以选择特定的字线和位线。字线和位线的交叉点是选定的存储单元。每个存储单元都是按照这种方法唯一选择的,然后进行读写操作。一些存储器设计为多个数据,如4位或8位,同时输入和输出。这样,将同时选择4个或8个存储单元进行读写操作。

在SRAM中,矩阵形式的存储单元阵型被翻译器和与外部信号的通信界面包围。存储单元阵型通常是方形或矩阵,以减少整个芯片面积,有利于数据存储。一个存储容量为4K位的SRAM例如,需要12条地址线来确保每个存储单元都能被选中(212=-4096)。如果存储单元阵型排列成只包括一列的长条,则需要12/4K位译码器,如果排成方形,包括64行和64列,那么只需要一个6/64位的行译码器和一个6/64位的行译码器。行、列译码器可分别排列在存储单元阵型的两侧。64行和64列有4096个交接点,每个点对应一个存储位置。

因此,将存储单元排列成方形比排列的长条应大大降低整个芯片的地面面积。除了奇特的形状和大范围外,存储单元排列成长条状的另一个缺点是,排列在排列上端的存储单元与数据输入/导出端之间的连接将变得非常长,特别是对于容积非常大的存储器,情况更为严重,连接延迟至少与其长度线性有关。连接时间越长,在线延迟就越大。因此,读写速度的降低和不同存储单元之间的连接延迟是不一致的,这是规划中需要避免的。

本文关键词:SRAM

相关文章:何为SRAM存储器静态随机存取